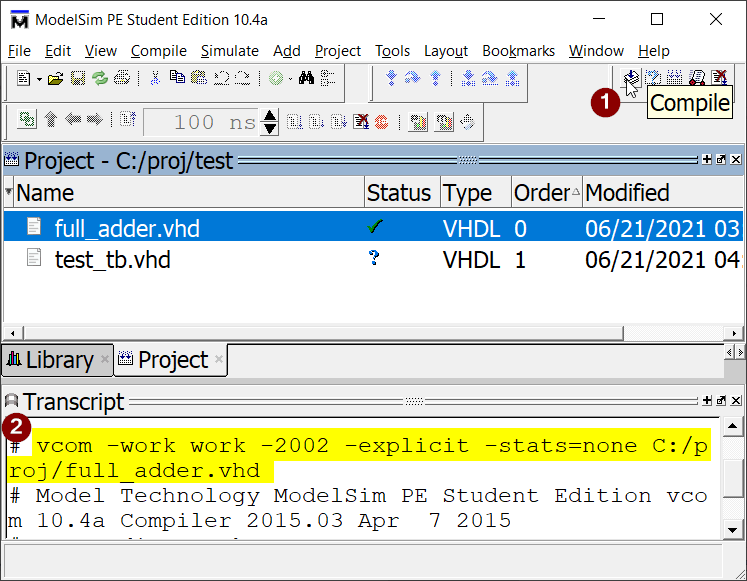

For example view signals To look at the signal variables. View * Observation includes signals、wave、dataflow And so on. Of course, you can also observe the results of other windows, use view Command display Īt this time, you can wave See your simulation results in the window file. run –all Command to keep the simulation going. Run 2000 The function of this command is to run 2000 A unit time simulation. Of course, you can also add a single signal, For example, add a clock :add waveclk wait. And then you can see wave The file was opened. Īdd wave/camera_tb/ * The purpose of this command is to testbench file camera_tb.v Middle module camera_tb Add all the signal variables to the waveform file, Pay attention to “*” Add a space before. Vsim camera_tb Simulation command, Note that the following parameters must be camera_tb.v The module name in the file. If so VHDL Files can be used vcom file1,file2 Command to compile. Vlog camera.v camera_tb.v The purpose of this command is to compile these files, Note that files can be compiled separately, But be sure to compile the called file first. Vmap work work The function of this command is to transfer the current logical working library work And the actual Repository work Mapping correspondence. Vlib work The function of this command is to create a work Catalog, Please be careful not to create a new one with the operating system work Folder, Because it's built with the operating system work The folder doesn't have ModelSim SE Automatically generated _info file. At the prompt, Run the following commands in sequence : Start-up ModelSimSE, The first thing to see is ModelSim SE The window on the right has ModelSim> Such a prompt. OdelSim Introduction to command line simulation Start emulating ,-c Option to vsim Working in commandline Pattern -l The option is output log File to vsim.log -do The option is to start the simulation and run tcl Script files -L The option is to specify the working logic library work.foo It's simulated top level module. vmap - Map the logical library name to the specified directory View error details : verror **( Wrong number )Ĭreate a logical library in the current directory work, After running, it will be found in the current directory work Folder. Exit simulation, Enter the command :quit –sim // Very often !!ħ. Add a signal to the waveform window, Enter the command :add wave -hex *, there * It means to add all the signals in the design ,-hex Represents the wave in hexadecimalĦ. Use do It's really convenient to simulate files, Than writing testbench It's much more convenient, use do The file doesn't have that many signal definitions, Management is also more convenient. Exit simulation, Enter the command :quit –sim.Ĭlassification : Verilog/FPGA 10:49 354 Human reading Comment on (1) Collection report

Start emulating, Enter the command ,run 3us, At this time, the simulation waveform appears in the waveform windowĦ. Add a signal to the waveform window, Enter the command :add wave -hex *, there * It means to add all the signals in the design ,-hex Represents the signal value in the waveform window in hexadecimal ĥ. Open the waveform window, Enter the command :view waveĤ.

#Modelsim 10 comman drivers

Add drivers to the clock signal, Enter the command :force clk 0 0,1 10 -r 20, Set the simulation clock to 50MHz ( Let the time unit be ns)ģ. Run the simulation, Enter the command in the main window :vsim work.

#Modelsim 10 comman how to

Use do It's really convenient to simulate files, Than writing testbench It's much more convenient, I have a deep feeling, At first, because I didn't know, Only know how to write testbence, In the small module also write testbench, I'm really upset ! And there's more to signal definition, use do There are not so many signal definitions in the file method, Management is also more convenient, ha-ha, It's really convenient, And in the form of a command line, It's a sense of accomplishment, ha-ha !ġ.

It's so simple modelsim Command line emulation Perhaps Xilinx Under the table of contents. (3) C:\Xilinx > compxlib -s mti_se -p c:\Modeltech_6.0\win32 -f all -l verilog -o C:\ Modeltech_6.0\Xilinx_lbis (2)“ function ” cmd, To xilinx Under the table of contents (1) Before loading, the modelsim.ini Change to not “ read-only ” Load the simulation tool with xilinx Library commands Vsim -assertdebug ScaleBlock_tf -L xilinxcorelib_ver -L unisims_ver // load xilinxlib libraryĤ. dump come outĪdd wavesim:/test/t/M2/Reg_out // Put the module Reg_out Medium waveform. Vsim -coverage -voptargs="+acc" -t ns test // The simulation file is test.vĪdd wave * // Put all the modules waveform. Vlog -cover bcest *.v // Compilation with coverage analysis Vlib work // establish work Simulation library

0 kommentar(er)

0 kommentar(er)